Binary counter

TLDRIn this educational video, the presenter explores the 74 LF 76 chip, which contains two built-in JK flip-flops. The video demonstrates how to set up the chip, highlighting its features such as the Q and Q inverted outputs, J and K inputs, and an inverted clock input that triggers on the falling edge. The presenter also explains the preset and clear inputs, which override the flip-flop state. A practical application is showcased by creating a divide-by-two circuit, which toggles the output at half the clock speed. This concept is expanded into a binary counter, illustrating how cascading JK flip-flops can be used to count in binary, demonstrating a fundamental principle in digital electronics.

Takeaways

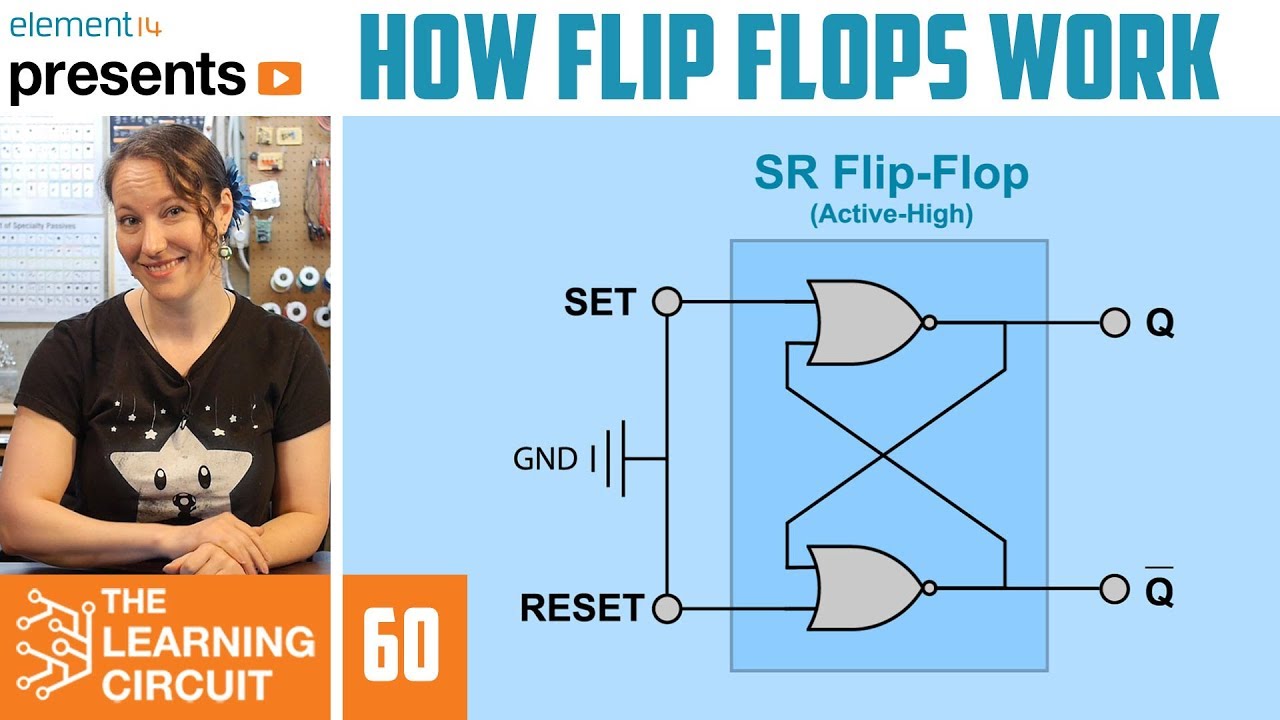

- 😀 The video discusses the challenges of building a JK flip-flop on a breadboard due to timing issues with edge detection.

- 🔍 The 74 LF 76 chip is introduced, which contains a built-in JK flip-flop, and the presenter aims to create a practical application with it.

- 📦 The 74 LF 76 chip has two JK flip-flops, each with Q and Q-bar (inverted Q) outputs, J and K inputs, and an inverted clock input.

- ⏲️ The flip-flops in the 74 LF 76 operate on a falling edge of the clock signal, which is a key timing consideration.

- 🔄 The chip also features preset and clear inputs, which can override the flip-flop state regardless of the clock or J and K inputs, but should be used with caution as they can lead to an unstable configuration.

- 🔌 The video shows a practical setup of the 74 LF 76 chip with VCC and ground for power, preset and clear inputs set high (inactive), and J and K inputs also set high.

- 🔄 Demonstration of the flip-flop toggling with each clock pulse, showing the Q and Q-bar outputs changing state.

- 🕒 The output frequency of the flip-flop is half the frequency of the input clock, which is why it can be referred to as a 'divide by two' circuit.

- 🔗 By cascading multiple flip-flops and using the output of one as the clock for the next, a binary counter is created, counting in binary from 0 to 15.

- 🛠️ The video concludes with an example of a binary counter made by connecting four 74 LF 76 chips, illustrating the concept of binary counting through division.

Q & A

What was the main challenge discussed in the last video regarding the JK flip-flop?

-The main challenge discussed in the last video was the difficulty in building a JK flip-flop on a breadboard due to the importance of timing around edge detection.

What is the 74 LF 76 chip and what does it contain?

-The 74 LF 76 is a chip that has two JK flip-flops built into it, which can be used to build practical or interesting circuits.

What are the two outputs provided by a JK flip-flop?

-A JK flip-flop provides two outputs: the Q output, which is the normal output, and the Q inverted output, which is the logical opposite of Q.

What is unique about the clock input on the 74 LF 76 chip?

-The clock input on the 74 LF 76 chip is an inverted clock, which means that the flip-flop switches states on the falling edge of the clock signal.

What are the preset and clear inputs on a JK flip-flop and how do they work?

-The preset and clear inputs on a JK flip-flop are used to override the clock and J and K inputs to directly set the output state. Preset, when low, forces the Q output high, and clear, when low, forces the output low. Both being low results in an invalid state that is non-stable and will not persist when the inputs return to their inactive high level.

Why is the configuration where both preset and clear inputs are low considered non-stable?

-The configuration where both preset and clear inputs are low is considered non-stable because it does not persist when the preset and/or clear inputs return to their inactive high level. It is an override meant for temporary state setting.

How does the JK flip-flop behave when both J and K inputs are set high?

-When both J and K inputs are set high, the JK flip-flop toggles its output with each clock pulse.

What is the effect of using the output of one flip-flop as the clock for another?

-Using the output of one flip-flop as the clock for another results in the second flip-flop toggling at half the speed of the first, effectively creating a divide-by-two operation.

Can you chain multiple JK flip-flops to create a binary counter?

-Yes, by chaining multiple JK flip-flops and using the output of one as the clock for the next, you can create a binary counter that counts in binary at a rate that is a fraction of the original clock speed.

What is the significance of the divide-by-two operation in the context of the video?

-The divide-by-two operation is significant because it demonstrates how the output of a JK flip-flop can be used to control the speed of another flip-flop, creating a cascading effect that can be used to build more complex circuits like binary counters.

Outlines

😀 Exploring the 74HC76 Chip and Building a Divided-by-Two Circuit

This paragraph discusses the challenges of building a JK flip-flop on a breadboard due to timing issues with edge detection. The presenter introduces the 74HC76 chip, which contains two built-in JK flip-flops. The explanation covers the pin functions, including the Q and Q' outputs, J and K inputs, inverted clock input, and preset and clear inputs. It highlights the inverted clock's role in toggling states on a falling edge and the use of preset and clear as overrides to set the output state. The video then demonstrates setting up the 74HC76 chip on a breadboard with VCC, ground, and inputs set high, showing the toggling behavior of the Q output with each clock pulse. The presenter also explains how cascading flip-flops can create a divided-by-two circuit, effectively halving the clock speed at each stage, and demonstrates this by connecting the output of one flip-flop to the clock input of another, creating a binary counter that counts in binary from 0 to 15.

😀 Binary Counting Demonstration with Cascaded Flip-Flops

In this brief paragraph, the presenter continues the demonstration of the binary counter created by cascading JK flip-flops from the 74HC76 chip. The video script simply states the numbers 14 and 15, indicating that the binary counter is counting up to these values, showcasing the practical application of the divided-by-two circuit concept discussed earlier. This step in the demonstration effectively illustrates how digital circuits can be used to perform basic counting operations in binary.

Mindmap

Keywords

💡JK flip-flop

💡74LF76

💡Edge detection

💡Output

💡Clock input

💡Preset and clear

💡Inverted clock

💡Divided by two

💡Binary counter

💡Cascading

Highlights

Introduction to the 74 LF 76 chip, which contains a built-in JK flip-flop.

The JK flip-flop's challenge in breadboard construction due to timing and edge detection.

74 LF 76 chip features two JK flip-flops, each with Q and Q inverted outputs.

J and K inputs are essential for the operation of the JK flip-flop.

Clock input is required and is inverted, meaning state changes on the falling edge.

Preset and clear inputs allow overriding the clock and setting the output state.

Active low nature of preset and clear inputs, indicated by the bubble symbol.

Invalid state occurs when both preset and clear are low, which is non-stable.

Setup of the 74 LF 76 chip with VCC and ground for power.

Preset and clear set high to be inactive, with J and K inputs also set high.

Clock pulse demonstration showing toggling of Q output with each pulse.

The divided by two effect where the output toggles at half the clock speed.

Creating a binary counter by cascading multiple flip-flops with their outputs feeding into the next flip-flop's clock.

Binary counting in action, demonstrating a 4-bit binary counter.

Observation of the binary counter's behavior at increased clock speeds.

Practical application of the 74 LF 76 chip in building a binary counter.

Transcripts

Browse More Related Video

5.0 / 5 (0 votes)

Thanks for rating: