Latches and Flip-Flops 1 - The SR Latch

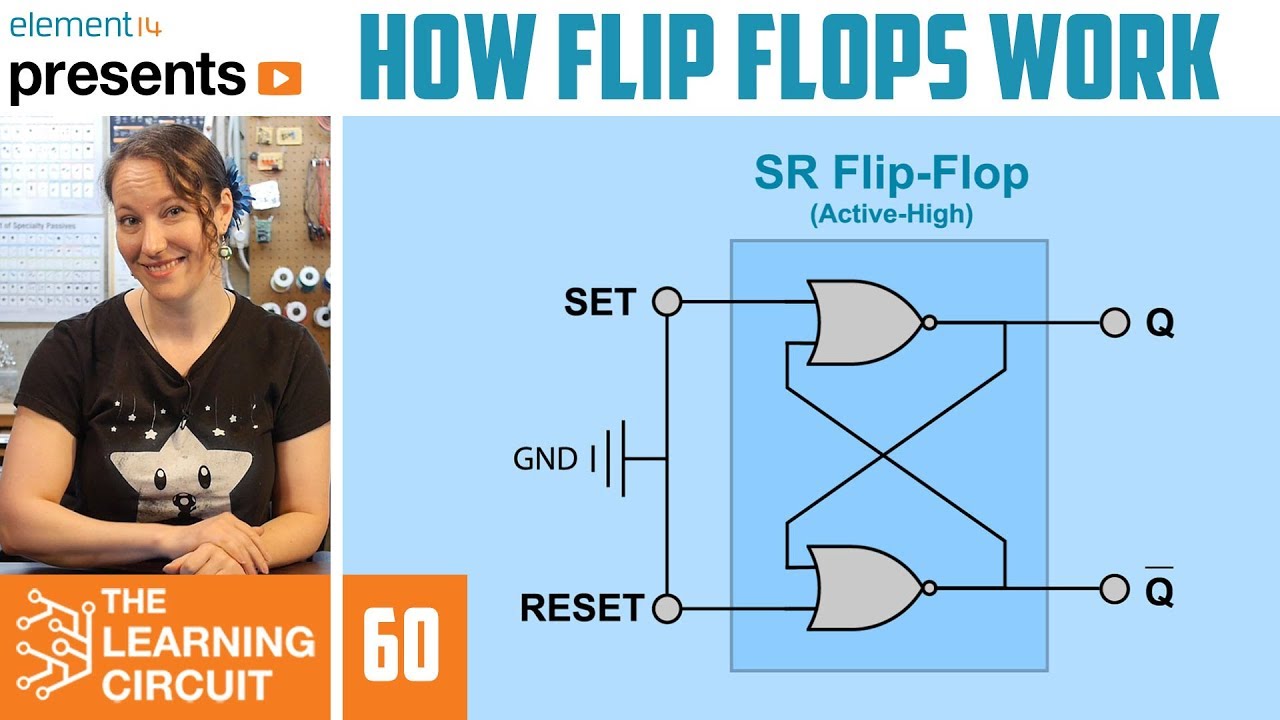

TLDRThis video script delves into the world of latches and flip-flops, focusing on the SR latch, a fundamental building block of computer memory. It explains how the SR latch, functioning as a one-bit memory, can be set or reset to stable states by input pulses and retains its state until changed again or power is removed. The script explores the construction of SR latches using NOR and NAND gates, highlighting the differences between active high and active low configurations. It also discusses the SR latch's application in debouncing mechanical switches and its role as a foundation for more complex memory circuits, providing a clear foundation for understanding memory storage in digital systems.

Takeaways

- 🌟 Latches and flip-flops are fundamental building blocks of computer memory.

- 🔄 The SR latch, or Set-Reset latch, acts as a one-bit memory that can be in one of two stable states, triggered by input pulses.

- 🔧 The SR latch remembers its state until changed by another input pulse or power removal, hence it's called a 'bistable' latch.

- 📚 Understanding of basic logic gates like OR, AND, NOR, and NAND is essential for constructing SR latches.

- 🔄 The SR latch can be constructed using either NOR or NAND gates, with each gate type creating a latch with different control mechanisms.

- 🔧 A NOR gate-based SR latch is an 'active high' latch, requiring high pulses to set or reset, while a NAND gate-based SR latch is 'active low'.

- 🔄 The SR latch has two inputs, R (reset) and S (set), and it can store a high or low output signal depending on the input pulses.

- 🚫 Both inputs S and R should not be high at the same time as it leads to an undefined state, which is considered illegal for the latch.

- 🛠 The SR latch can be used to debounce mechanical switches, providing a single, clean signal from multiple on-off signals.

- 🔐 The SR latch is useful in control applications where conditions may change and need to be monitored and reacted to accordingly.

- 🏗️ The SR latch is a foundational component in the creation of more complex memory circuits.

Q & A

What are latches and flip-flops in the context of computer memory?

-Latches and flip-flops are fundamental building blocks of computer memory. They are used to store data, with latches being simpler and flip-flops being more complex and stable storage elements.

What is an SR latch?

-An SR latch, also known as a Set-Reset latch, is a type of latch that can be thought of as a one-bit memory. It has two inputs, Set (S) and Reset (R), and can be put into one of two stable output states triggered by an input pulse.

How does an SR latch remember its state?

-An SR latch remembers its state through positive feedback created by the cross-coupling of its gates. It maintains the state until it's changed again by another input pulse or until power is removed.

What are the two types of basic logic gates mentioned in the script?

-The two types of basic logic gates mentioned are the OR gate and the AND gate. They are fundamental components used in constructing more complex circuits like the SR latch.

What is the purpose of inverting the output of an OR gate with a NOT gate?

-Inverting the output of an OR gate with a NOT gate allows for swapping the zeros for ones and ones for zeros in the output column of the truth table, creating a NOR gate which only produces an output of one if both inputs are zero.

How are the two NOR gates connected in an SR latch built from NOR gates?

-In an SR latch built from NOR gates, the two NOR gates are connected in a cross-coupled manner, where the output of each NOR gate is one of the inputs of the other gate.

What happens when a reset pulse is applied to an SR latch?

-When a reset pulse is applied to an SR latch, it changes the output of the top gate, which is then fed back into the lower gate, causing the latch to store a zero.

What is the forbidden state for an SR latch built from NAND gates?

-The forbidden state for an SR latch built from NAND gates is when both S and R are simultaneously zero, which would result in an illegal state where both Q and its complement are one.

How does an SR latch help in debouncing a mechanical switch?

-An SR latch helps in debouncing a mechanical switch by ignoring any further set signals after it has already been set, thus providing a clean, single signal transition despite multiple on-off signals generated by switch bounce.

What is the difference between an active high and an active low SR latch?

-An active high SR latch is set or reset with high logic levels, meaning a high pulse at one of the inputs is required to change the state. An active low SR latch, on the other hand, is set or reset with low logic levels, requiring a low pulse at one of the inputs to change the state.

What is the significance of the SR latch in building more sophisticated memory circuits?

-The SR latch is significant as it serves as the building block of more sophisticated memory circuits. Its ability to store and change states based on input pulses makes it a fundamental component in the design of complex memory systems.

Outlines

🔒 Introduction to SR Latches and Basic Logic Gates

This paragraph introduces the concept of SR latches, which are fundamental components of computer memory. It explains that an SR latch can be considered as a one-bit memory capable of holding one of two stable output states, triggered by an input pulse. The latch remembers its state until changed by another pulse or power removal. The paragraph also reviews basic logic gates, such as the OR and AND gates, and their inverted versions, the NOR and NAND gates, which are essential for constructing SR latches. The SR latch can be built using either NOR or NAND gates, with the cross-coupling of these gates leading to positive feedback and enabling the latch to maintain its state. The paragraph also describes the initial state of the SR latch with both inputs low and the output high, and how applying a reset pulse to input R changes the state to store a zero.

🔄 SR Latch Operation and Truth Table Analysis

This section delves into the operation of the SR latch, emphasizing its control through pulses rather than continuous high inputs, which results in a unique truth table. The latch has two inputs, S and R, and can be in a set or reset state, with output Q and its inverse, not Q, being opposites. The paragraph explains the process of resetting and setting the latch using pulses on inputs S and R, respectively. It also highlights the forbidden state where both S and R are high simultaneously, as this leads to an indeterminate state and is considered illegal. The paragraph concludes by contrasting the active-high SR latch built from NOR gates with the active-low SR latch built from NAND gates, noting their different behaviors and truth tables.

🛠 Applications of SR Latches and Debouncing Mechanism

The final paragraph discusses the practical applications of SR latches, particularly in control systems where conditions may change and require a response. It also addresses the issue of switch bounce, where a mechanical switch can generate multiple electrical signals in a short time, potentially causing problems for the controlled circuit. An integrated circuit with an SR latch can be used to debounce such signals, ensuring that only one signal is recognized even if the switch generates multiple signals. The paragraph provides an example of how an SR latch can be used to debounce a signal from a mechanical switch, changing the output from low to high when the switch is pressed. It also suggests other applications, such as in a burglar alarm system, where the SR latch can help maintain the alarm state once triggered. The paragraph concludes by noting the SR latch's role as a building block for more complex memory circuits.

Mindmap

Keywords

💡Latches

💡Flip-Flops

💡SR Latch

💡Stable Output States

💡Input Pulse

💡Logic Gates

💡NOR Gate

💡NAND Gate

💡Debounce

💡Active High

💡Active Low

💡Race Condition

Highlights

Latches and flip-flops are fundamental building blocks of computer memory.

The SR latch acts as a one-bit memory with stable output states triggered by input pulses.

An SR latch remembers its state until changed by another input pulse or power removal.

Basic logic gates such as OR, AND, NOR, and NAND are essential for constructing SR latches.

An SR latch can be constructed using either NOR or NAND gates for its operation.

The cross-coupling of NOR gates in an SR latch creates positive feedback.

The SR latch has two inputs, R and S, and provides the output Q and its inverse, not Q.

Applying a reset pulse to input R changes the latch's state from storing one to zero.

A set pulse at input S forces the latch into a set state regardless of the previous state.

The SR latch's truth table is unique due to its control by pulses rather than continuous inputs.

Both inputs S and R should never be high simultaneously to avoid an undefined state.

An SR latch built with NAND gates is known as an active low SR latch.

The NAND gate-based SR latch has a forbidden state when both S and R are zero.

SR latches are used in control applications to monitor and react to changing conditions.

An SR latch can debounce signals from mechanical switches, preventing unwanted effects.

The SR latch serves as a building block for more sophisticated memory circuits.

Transcripts

5.0 / 5 (0 votes)

Thanks for rating: