How Flip Flops Work - The Learning Circuit

TLDRIn this educational video, the concept of flip-flops, a type of sequential logic device, is explored. Unlike combinational logic devices, flip-flops have memory capabilities and can use current and previous input data. The video explains the basic SR flip-flop, its active high and low variants, and how it can be modified with gating. It also introduces D-type and JK flip-flops, highlighting the clock signal's role and the issue of invalid states in D-type flip-flops, which JK flip-flops solve by toggling the output. The video encourages viewers to learn more about additional inputs like preset and clear, and to engage with the community on element14.com for further exploration.

Takeaways

- 🔌 Element14 is an electronics community for engineers to connect and collaborate.

- 🔍 The video is about flip-flops, which are sequential logic devices with memory.

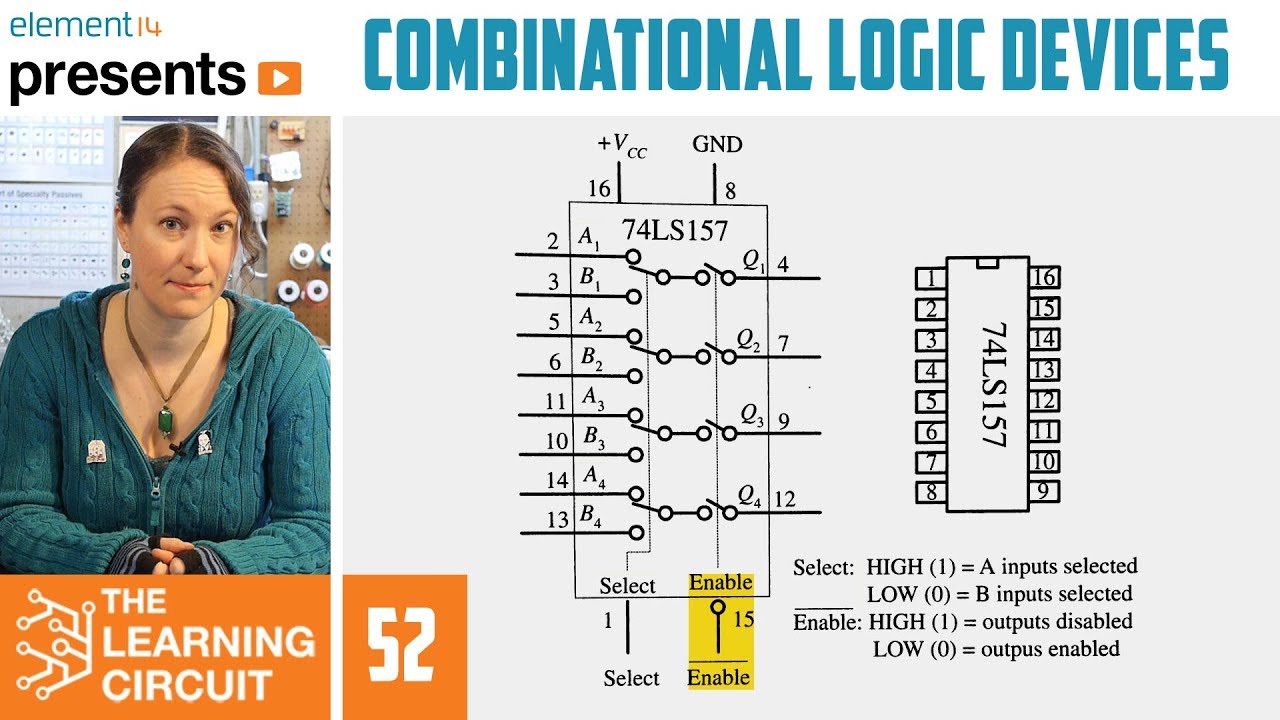

- 💡 Flip-flops differ from combinational logic devices, which rely only on current inputs.

- 🧠 Flip-flops can store previous input data, allowing them to have two states: logic level 0 or 1.

- 🔀 SR flip-flops have two inputs (Set and Reset) and two outputs (Q and Not Q).

- 🔄 SR flip-flops can be active high or active low, affecting how they respond to input changes.

- ⚙️ Active high SR flip-flops use NOR gates, while active low SR flip-flops use NAND gates.

- 🔄 Gated SR latches add AND gates to control the inputs, enabling them only when a certain condition is met.

- ⏲️ D-type and JK flip-flops introduce a clock signal to synchronize changes in output with the clock pulse.

- 🛠️ JK flip-flops solve the invalid state problem found in SR flip-flops by using three-input NAND gates.

Q & A

What is the primary focus of the video 'The Learning Circuit'?

-The primary focus of the video is to teach about flip-flops, which are sequential logic devices used in electronics.

What are flip-flops in the context of electronics?

-Flip-flops are logic devices that have a form of memory built in, allowing them to use current and previous input data to determine their output.

What distinguishes sequential logic devices like flip-flops from combinational logic devices?

-Sequential logic devices have memory and can use previous input data, whereas combinational logic devices output solely based on the current state of their inputs.

What are the two states that flip-flops can be in?

-Flip-flops can be in one of two states: a logic level 0 or a logic level 1.

What are the typical labels for the inputs and outputs of an SR flip-flop?

-The inputs are labeled S (set) and R (reset), and the outputs are labeled Q and not Q (Q Bar).

How does an active high SR flip-flop made of NOR gates operate?

-In an active high SR flip-flop, the inputs are normally low. When the set input goes high, it sets the latch and output Q goes high. The output Q remains high until the reset input goes high, resetting the output to low.

What happens in an SR flip-flop if both set and reset inputs are active at the same time?

-If both set and reset inputs are active simultaneously, an invalid state is triggered, causing the flip-flop to lose control of the outputs and making their future states unpredictable.

What is the difference between active high and active low SR flip-flops?

-In an active high SR flip-flop, the inputs are normally low and go high when active. In an active low SR flip-flop, the inputs are normally high and go low when active.

How does the clock signal influence D-type and JK flip-flops?

-The clock signal in D-type and JK flip-flops acts as an enable pin, allowing the data input to affect the output in sync with the clock pulses. The clock signal can trigger outputs to change states on the rising or falling edge of the clock pulse.

What issue does the JK flip-flop solve compared to the SR flip-flop?

-The JK flip-flop solves the issue of the invalid state in SR flip-flops by using three-input NAND gates. If both J and K inputs are high, the output toggles instead of entering an invalid state.

What are some additional inputs you might find on flip-flop ICs and what should you do to understand them?

-You might find inputs like preset and clear on flip-flop ICs. It is suggested to research and understand what these inputs do and how they work in the sequence.

Outlines

🔌 Introduction to Flip-Flops and SR Latch Basics

The video script introduces the concept of flip-flops, a type of logic device used in integrated circuits (ICs), with a focus on the SR flip-flop, also known as an SR latch. It explains that flip-flops are sequential logic devices that incorporate memory, allowing them to use both current and previous input data. The SR flip-flop has two inputs, set (S) and reset (R), and two outputs, Q and its inverse, not Q. The script clarifies the difference between active high and active low configurations and provides an example of an SR flip-flop made with NOR gates, detailing its operation and the significance of its interconnected design. It also touches on the invalid state that can occur when both set and reset inputs are active simultaneously, which is a critical issue to be addressed later in the script.

🕒 Understanding Gated SR Latches and Advanced Flip-Flop Types

This paragraph delves into gated SR latches and their operation, where an enable input is introduced to control the set and reset inputs through AND gates. The enable input must be active for the set and reset to influence the outputs, providing an additional layer of control. The script then transitions to discussing D-type and JK flip-flops, which include a clock signal input for synchronous operation. It explains how the clock signal acts as an enable for the data input, allowing the output to change state with each clock pulse. The script also highlights the differences between asynchronous set and reset inputs, which have priority over the clock signal, and synchronous data inputs, which must wait for the next clock pulse. The paragraph concludes with an explanation of the invalid state problem in D-type flip-flops and how JK flip-flops, with their additional NAND gates, solve this issue by toggling the output when both J and K inputs are active high, thus eliminating the invalid state.

Mindmap

Keywords

💡Flip-flops

💡Sequential Logic Devices

💡Logic Gates

💡SR Flip-Flop

💡Active High and Active Low

💡Gated SR Latch

💡Clock Signal

💡D-Type Flip-Flop

💡JK Flip-Flop

💡Invalid State

💡Preset and Clear

Highlights

Introduction to flip-flops, a type of logic device packaged into ICs, not the footwear.

Explanation of sequential logic devices, including flip-flops, which have memory and use current and previous data.

Flip-flops are bistable devices with outputs that can be at logic level 0 or 1.

Basic construction of flip-flops using logic gates, essential for understanding their function.

Introduction to the SR flip-flop, a basic sequential logic circuit with set and reset inputs.

Description of SR flip-flop outputs Q and not Q, and their inverse relationship.

Active high and active low configurations of SR flip-flops and their behavior.

Logic diagram explanation of SR flip-flop made with NOR gates, active high.

Functioning of SR flip-flop with set and reset inputs, and the latching mechanism.

Invalid state problem when set and reset inputs are active simultaneously in SR flip-flops.

Active low SR flip-flop made with NAND gates and its operation.

Introduction to gated SR latches and their enable input functionality.

Understanding of D-type and JK flip-flops, which include a clock signal input.

Clock signal's role in enabling flip-flop triggering and data input synchronization.

Asynchronous set and reset inputs in flip-flops and their priority over the clock signal.

Problem of invalid states in D-type flip-flops when set and reset are active simultaneously.

JK flip-flop's solution to the invalid state problem with its toggle functionality.

Homework assignment to explore additional flip-flop inputs like preset and clear.

Invitation to report findings and discuss in the Element14 community.

Transcripts

5.0 / 5 (0 votes)

Thanks for rating: